# IMPROVING STUDENT COMPREHENSION THROUGH INTERACTIVE MICROARCHITECTURE SIMULATION AND VISUALIZATION

A Thesis by ANDREW BROWNFIELD

Submitted to the Graduate School at Appalachian State University in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE

> December 2013 Department of Computer Science

# IMPROVING STUDENT COMPREHENSION THROUGH INTERACTIVE MICROARCHITECTURE SIMULATION AND VISUALIZATION

A Thesis by ANDREW BROWNFIELD December 2013

## APPROVED BY:

Dr. Cindy Norris Chairperson, Thesis Committee

Professor Frank Barry Member, Thesis Committee

Dr. Alice McRae Member, Thesis Committee

Dr. James T. Wilkes Chairperson, Computer Science

Edelma D. Huntley Dean, Research and Graduate Studies Copyright by Andrew Brownfield 2013 All Rights Reserved

### Abstract

## IMPROVING STUDENT COMPREHENSION THROUGH INTERACTIVE MICROARCHITECTURE SIMULATION AND VISUALIZATION.

Andrew Brownfield B.S., Appalachian State University M.S., Appalachian State University

Chairperson: Dr. Cindy Norris

The curricula of most Computer Science departments include at least one course on computer organization and assembly language. The seminal concepts covered by such courses bridge the gap between hardware and software by introducing multiple layers of abstraction. Appalachian State University introduces this material in the course "Introduction to Computer Systems." The current structure of the course teaches the concepts using the hypothetical LC-3 processor, as presented in Patt and Patel's textbook "Introduction to Computing Systems: From Bits & Gates to C & Beyond (2nd edition)." Prior to the completion of the work presented in this thesis, tools existed for the assembly of LC-3 programs and simulation of the assembled code; however, no simulator existed to demonstrate the function of the microarchitectural level.

In this thesis, research on educational simulators is presented, with an emphasis on microarchitectural and graphical style simulators. Multiple simulators were reviewed to determine which elements are pedagogically effective and which elements detract from the educational value of the simulator. Based on these findings, a graphical microarchitecture simulator named lc3uarch was implemented. The simulator targets the microarchitectural level of the LC-3 processor. To determine its effectiveness as an educational tool, student surveys were conducted. The responses indicated that the use of lc3uarch can help students comprehend the logic components of the LC-3 microarchitecture and provided ideas for making the tool more effective.

### Acknowledgments

If it weren't for the support of many people, this thesis would not have come to fruition. Foremost, many thanks to my advisor, Dr. Norris. In spite of my lethargic pace, she did not lose hope that I would eventually finish. Many thanks also go to the thesis committee members Professor Barry and Dr. McRae.

As the graduate school liaison, Dr. Fenwick has been a great help in enrollment, scheduling issues, and ensuring that the deadline had not passed.

My deepest gratitude goes to my family. Their words of encouragement and eagerness to provide childcare have been a boon in finishing. My amazing wife Erin has been my biggest cheerleader, particularly during times of self doubt and in the final weeks of writing.

# Dedication

This thesis is dedicated to my son, Dayton Robert Brownfield. On many occasions he attempted to help write the paper. In spite of his best efforts, the following is the only contribution that will make the final cut: "vnuhn7k7ufjk..g...v..g..gg/f.vbv/gb/// t,,g,g,ggggggg."

# Table of Contents

| Dedication       vii         List of Figures       xi         List of Tables       xii         List of Tables       xii         Foreword       xiii         1       Introduction       1         2       Uses of Simulation and Visualization       4         2.1       Advantages of Simulators       5         2.2       Use of Simulators for Education       8         2.2.1.1       Introduction to Computer Science       9         2.2.1.2       Introduction to Computer Organization       9         2.2.1.3       Advanced Computer Organization       12         2.2.2       Pedagogical Styles and the Use of Simulators       13         2.3       Simulation Visualization and Interfaces       14         2.4       Taxonomy and Categories of Educational Simulators       16         2.4.1       Historical       17         2.4.1.2       Digital Logic       17         2.4.1.3       Simple Hypothetical Simulators       18         2.4.1.4       Intermediate Instruction Set       18         2.4.1.5       Advanced Microarchitecture Simulators       18         2.4.1.6       Multiprocessor       19         2.4.2.1       Scope                                                                             | Abstrac    | t                                  |                                                                                                                        |                                      | iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures       xi         List of Tables       xii         Foreword       xiii         1 Introduction       1         2 Uses of Simulation and Visualization       4         2.1 Advantages of Simulators       5         2.2 Use of Simulators for Education       8         2.2.1.1 Introduction to Computer Science       9         2.2.1.2 Introduction to Computer Organization       12         2.2.2 Pedagogical Styles and the Use of Simulators       13         2.3 Simulation Visualization and Interfaces       14         2.4 Taxonomy and Categories of Educational Simulators       16         2.4.1.1 Historical       17         2.4.1.3 Simple Hypothetical Simulators       17         2.4.1.4 Intermediate Instruction Set       18         2.4.1.5 Advanced Microarchitecture Simulators       18         2.4.1.6 Multiprocessor       19         2.4.1.7 Memory Simulators       20         2.4.2.1 Scope       20                                                                                                                                                                                                                                                                                         | Acknow     | ledgmer                            | nts                                                                                                                    |                                      | vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| List of Tables       xii         Foreword       xiii         1       Introduction       1         2       Uses of Simulation and Visualization       4         2.1       Advantages of Simulators       5         2.2       Use of Simulators for Education       8         2.2.1       Targeted Courses       8         2.2.1.1       Introduction to Computer Science       9         2.2.1.2       Introduction to Computer Organization       9         2.2.1.2       Introduction to Computer Organization       12         2.2.2       Pedagogical Styles and the Use of Simulators       13         2.3       Simulation Visualization and Interfaces       14         2.4       Taxonomy and Categories of Educational Simulators       16         2.4.1       Historical       17         2.4.1.1       Historical       17         2.4.1.2       Digital Logic       17         2.4.1.3       Simple Hypothetical Simulators       18         2.4.1.4       Intermediate Instruction Set       18         2.4.1.5       Advanced Microarchitecture Simulators       18         2.4.1.6       Multiprocessor       19         2.4.2.1       Scope       20 </td <td>Dedicat</td> <td>ion</td> <td></td> <td></td> <td>vii</td> | Dedicat    | ion                                |                                                                                                                        |                                      | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Foreword       xiii         1       Introduction       1         2       Uses of Simulation and Visualization       4         2.1       Advantages of Simulators       5         2.2       Use of Simulators for Education       8         2.2.1       Targeted Courses       8         2.2.1.1       Introduction to Computer Science       9         2.2.1.2       Introduction to Computer Organization       9         2.2.1.3       Advanced Computer Organization       12         2.2.2       Pedagogical Styles and the Use of Simulators       13         2.3       Simulation Visualization and Interfaces       14         2.4       Taxonomy and Categories of Educational Simulators       16         2.4.1       Historical       17         2.4.1.2       Digital Logic       17         2.4.1.4       Intermediate Instruction Set       18         2.4.1.5       Advanced Microarchitecture Simulators       18         2.4.1.6       Multiprocessor       19         2.4.1.7       Memory Simulators       20         2.4.2       Taxonomy of Program Visualizations       20                                                                                                                                         | List of I  | Figures                            |                                                                                                                        |                                      | xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1       Introduction       1         2       Uses of Simulation and Visualization       4         2.1       Advantages of Simulators       5         2.2       Use of Simulators for Education       8         2.2.1       Targeted Courses       8         2.2.1       Introduction to Computer Science       9         2.2.1.1       Introduction to Computer Organization       9         2.2.1.2       Introduction to Computer Organization       12         2.2.2       Pedagogical Styles and the Use of Simulators       13         2.3       Simulation Visualization and Interfaces       14         2.4       Taxonomy and Categories of Educational Simulators       16         2.4.1       Categories of Simulators       16         2.4.1.1       Historical       17         2.4.1.2       Digital Logic       17         2.4.1.3       Simple Hypothetical Simulators       17         2.4.1.4       Intermediate Instruction Set       18         2.4.1.5       Advanced Microarchitecture Simulators       18         2.4.1.6       Multiprocessor       19         2.4.1.7       Memory Simulators       20         2.4.2       Taxonomy of Program Visualizations       20     <                                    | List of 7  | Tables .                           |                                                                                                                        |                                      | xii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2       Uses of Simulation and Visualization       4         2.1       Advantages of Simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Forewor    | d                                  |                                                                                                                        |                                      | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1       Advantages of Simulators       5         2.2       Use of Simulators for Education       8         2.2.1       Targeted Courses       8         2.2.1.1       Introduction to Computer Science       9         2.2.1.2       Introduction to Computer Organization       9         2.2.1.3       Advanced Computer Organization       12         2.2.2       Pedagogical Styles and the Use of Simulators       13         2.3       Simulation Visualization and Interfaces       14         2.4       Taxonomy and Categories of Educational Simulators       16         2.4.1       Historical       17         2.4.1.2       Digital Logic       17         2.4.1.3       Simple Hypothetical Simulators       18         2.4.1.4       Intermediate Instruction Set       18         2.4.1.5       Advanced Microarchitecture Simulators       19         2.4.1.7       Memory Simulators       20         2.4.2       Taxonomy of Program Visualizations       20                                                                                                                                                                                                                                                       | 1 Intro    | oductior                           | 1                                                                                                                      |                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.4Taxonomy and Categories of Educational Simulators162.4.1Categories of Simulators162.4.1.1Historical172.4.1.2Digital Logic172.4.1.3Simple Hypothetical Simulators172.4.1.4Intermediate Instruction Set182.4.1.5Advanced Microarchitecture Simulators182.4.1.6Multiprocessor192.4.1.7Memory Simulators202.4.2Taxonomy of Program Visualizations202.4.2.1Scope20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.1<br>2.2 | Advant<br>Use of<br>2.2.1<br>2.2.2 | tages of S<br>Simulato<br>Targeted<br>2.2.1.1<br>2.2.1.2<br>2.2.1.3<br>Pedagog                                         | Simulators                           | $     \begin{array}{r}       4 \\       5 \\       8 \\       9 \\       9 \\       9 \\       12 \\       13 \\     \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $2.4.2.2  \text{Abstraction}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -          | Taxono<br>2.4.1                    | omy and<br>Categori<br>2.4.1.1<br>2.4.1.2<br>2.4.1.3<br>2.4.1.4<br>2.4.1.5<br>2.4.1.6<br>2.4.1.7<br>Taxonon<br>2.4.2.1 | Categories of Educational Simulators | $     \begin{array}{r}       16 \\       16 \\       17 \\       17 \\       17 \\       18 \\       18 \\       19 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\       20 \\$ |

|   |      |         | 2.4.2.3    | Specification                                                            |   | • |       | 21       |

|---|------|---------|------------|--------------------------------------------------------------------------|---|---|-------|----------|

|   |      |         | 2.4.2.4    | Interface                                                                |   | • |       | 22       |

|   |      |         | 2.4.2.5    | Presentation                                                             |   | • |       | 22       |

|   |      | 2.4.3   | Taxonon    | y of Architecture Visualization                                          |   | • |       | 23       |

|   |      |         | 2.4.3.1    | Scope of Operation                                                       |   | • |       | 23       |

|   |      |         | 2.4.3.2    | Content Modeling                                                         |   |   |       | 23       |

|   |      |         | 2.4.3.3    | Presentation Methods                                                     |   |   |       | 24       |

|   |      |         | 2.4.3.4    | Activity Style                                                           |   |   |       | 24       |

|   |      |         |            |                                                                          |   |   |       |          |

| 3 |      | -       |            |                                                                          |   |   |       | 26       |

|   | 3.1  |         | •          | nulators                                                                 |   |   |       | 26       |

|   |      | 3.1.1   |            | Switch Computer                                                          |   |   |       | 27       |

|   |      | 3.1.2   |            | an Computer (LMC)                                                        |   |   |       | 29       |

|   |      | 3.1.3   | EasyCP     | J                                                                        |   | • |       | 30       |

|   | 3.2  | Digita  | l Logic Si | nulators                                                                 |   | • |       | 32       |

|   |      | 3.2.1   | Logisim    |                                                                          |   | • |       | 33       |

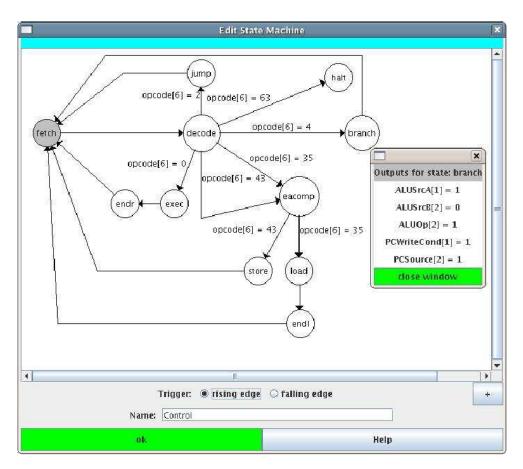

|   |      | 3.2.2   | DLSim 3    |                                                                          |   | • |       | 35       |

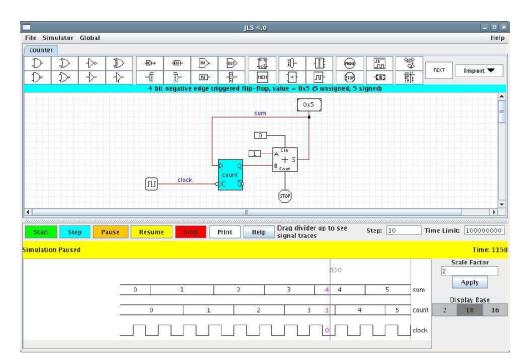

|   |      | 3.2.3   | JLS        |                                                                          |   | • |       | 36       |

|   | 3.3  | Microa  | architectu | e Simulators                                                             |   | • |       | 37       |

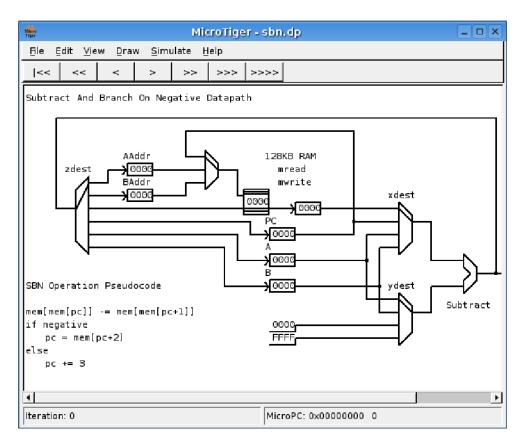

|   |      | 3.3.1   |            | er                                                                       |   |   |       | 37       |

|   |      | 3.3.2   |            | ,<br>J                                                                   |   |   |       | 40       |

|   |      | 3.3.3   | -          | 1                                                                        |   |   |       | 42       |

|   |      | 3.3.4   |            |                                                                          |   |   |       | 43       |

|   |      | _       |            |                                                                          |   |   |       |          |

| 4 | LC-: |         |            |                                                                          |   |   |       | 45       |

|   | 4.1  | Instru  |            | Architecture                                                             |   |   |       | 45       |

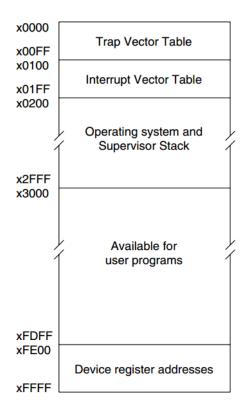

|   |      | 4.1.1   | •          |                                                                          |   |   |       | 46       |

|   |      | 4.1.2   | Registers  |                                                                          |   | • | <br>• | 46       |

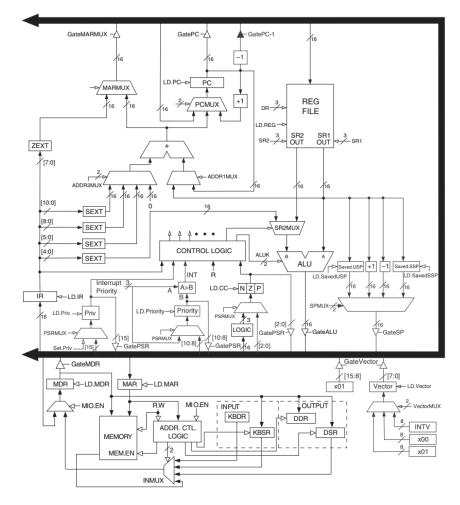

|   |      | 4.1.3   | -          | s and Exceptions                                                         |   |   |       | 48       |

|   |      | 4.1.4   | Instructi  | cons                                                                     |   | • |       | 48       |

|   | 4.2  | Microa  | architectu | e                                                                        |   | • |       | 51       |

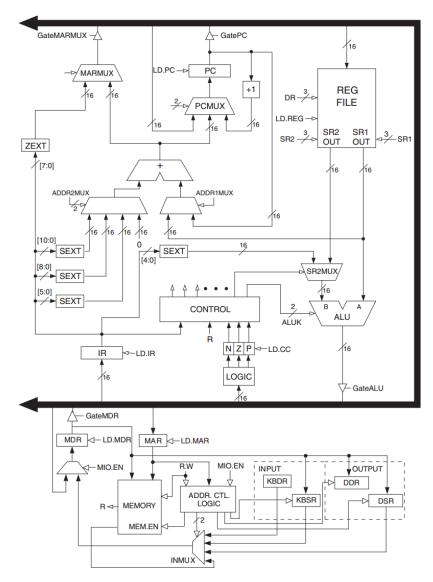

|   |      | 4.2.1   | Datapat    | 1                                                                        |   | • |       | 51       |

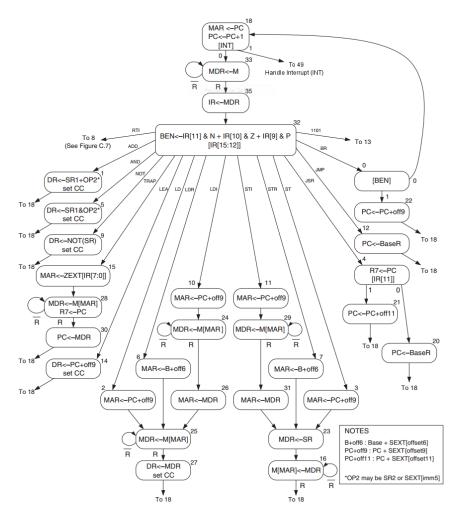

|   |      | 4.2.2   | Control    |                                                                          |   | • |       | 55       |

|   | 4.3  | Existin | ng Project | s                                                                        |   | • |       | 57       |

| 5 | Doci | an ond  | Implome    | tation                                                                   |   |   |       | 59       |

| 9 |      | 0       | -          |                                                                          |   |   |       |          |

|   | 5.1  | 0       | 0          | mulator                                                                  |   |   |       | 59<br>60 |

|   | FO   |         |            | ty and Language Choice                                                   |   |   |       | 60       |

|   | 5.2  |         | 0          | onomy and Categories                                                     |   |   |       | 61       |

|   | 5.3  | 0       |            |                                                                          |   |   |       | 64       |

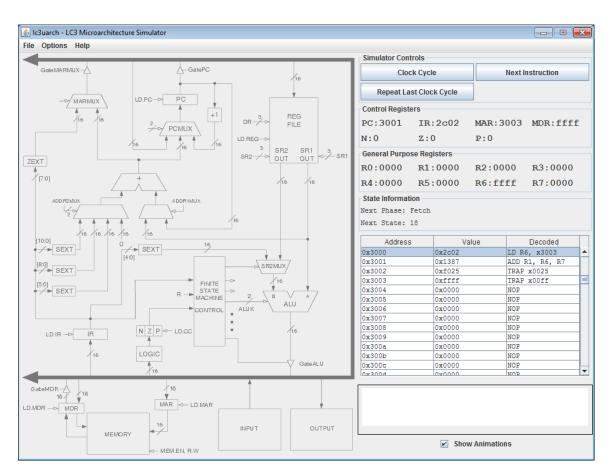

|   | 5.4  | Graph   | ical Imple | mentation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | • | • | <br>• | 65       |

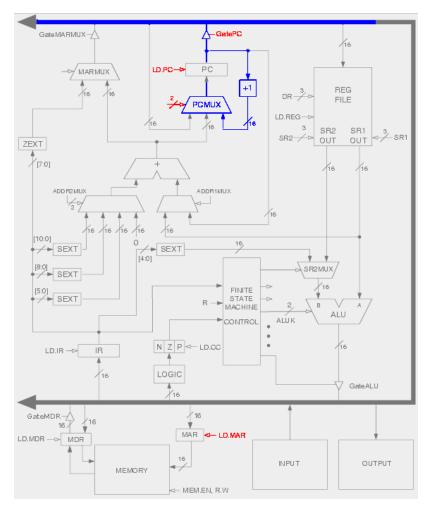

|                               |       | 5.4.1<br>5.4.2 | Animated Datapath65Controls and Components68                             |  |

|-------------------------------|-------|----------------|--------------------------------------------------------------------------|--|

| 6                             | Eval  | uation .       | 73                                                                       |  |

|                               | 6.1   | Survey         | Content                                                                  |  |

|                               | 6.2   | Result         | of Surveys                                                               |  |

| 7 Conclusions and Future Work |       |                |                                                                          |  |

|                               | 7.1   | Conclu         | sions $\ldots$ $\ldots$ $\ldots$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ |  |

|                               | 7.2   | Future         | Work                                                                     |  |

|                               |       | 7.2.1          | Graphical and Usability Changes                                          |  |

|                               |       | 7.2.2          | Pedagogical Enhancements                                                 |  |

|                               |       | 7.2.3          | Extended Scope                                                           |  |

| Re                            | feren | ces            |                                                                          |  |

| Vi                            | ta .  |                | 88                                                                       |  |

# List of Figures

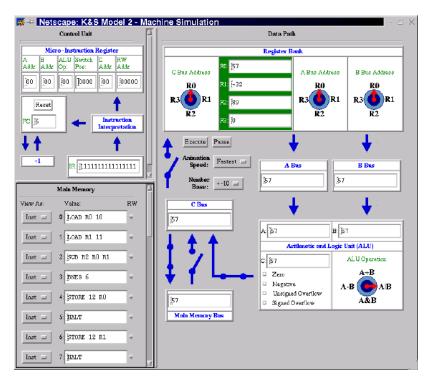

| 3.1  | First Stage of Knob & Switch Simulator |

|------|----------------------------------------|

| 3.2  | Final Stage of Knob & Switch Simulator |

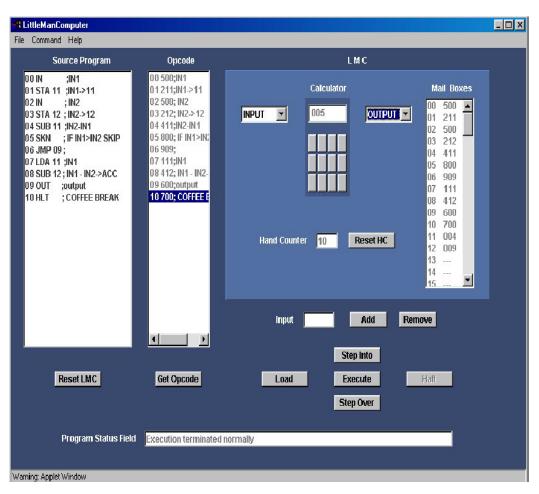

| 3.3  | Little Man Computer                    |

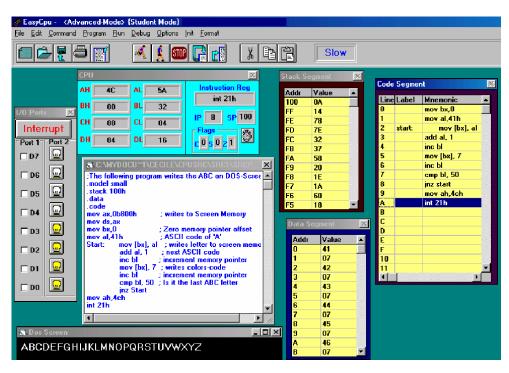

| 3.4  | EasyCPU Basic-Mode                     |

| 3.5  | EasyCPU Advanced-Mode                  |

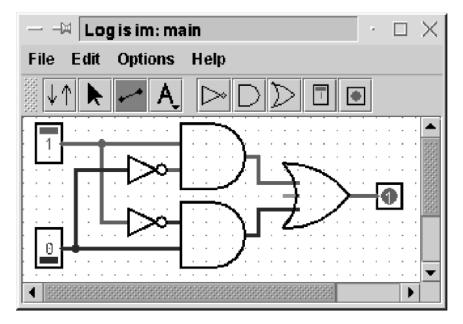

| 3.6  | Logisim Editor                         |

| 3.7  | DLSim 3                                |

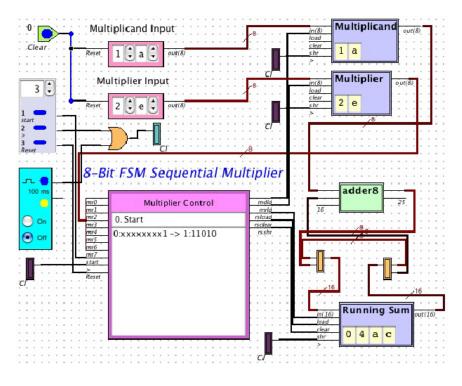

| 3.8  | JLS Circuit Editor                     |

| 3.9  | JLS FSM Editor                         |

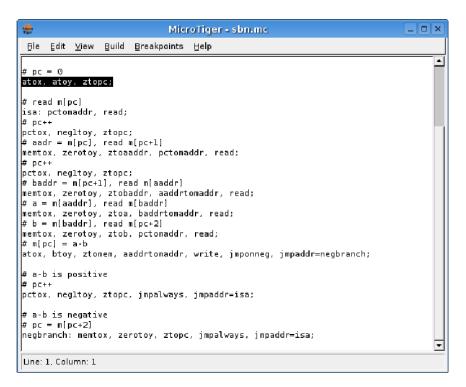

| 3.10 | MicroTiger Datapath Editor             |

| 3.11 | MicroTiger Microcode Editor            |

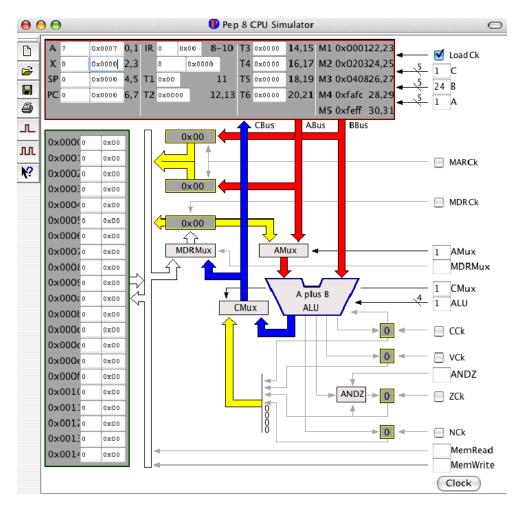

| 3.12 | Pep8CPU Datapath                       |

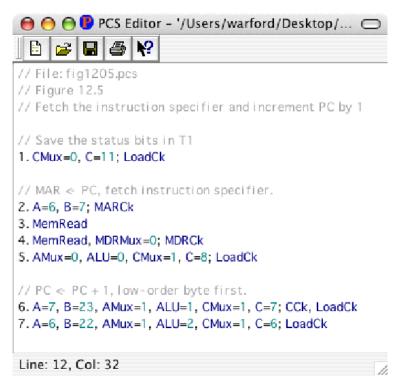

|      | Pep8CPU Microcode Editor               |

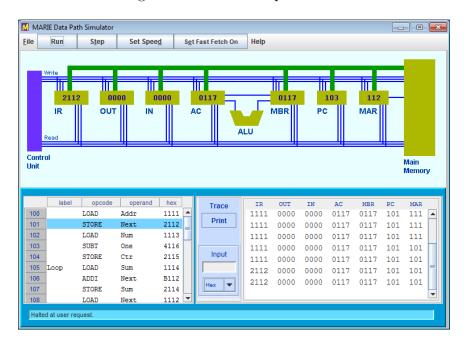

|      | MarieSim Datapath                      |

| 3.15 | RTLSim Datapath                        |

| 11   | LC-3 Memory Lavout                     |

| 4.1  |                                        |

| 4.2  | LC-3 Instructions                      |

| 4.3  | LC-3 Basic Datapath                    |

| 4.4  | LC-3 Datapath with Interrupts          |

| 4.5  | LC-3 Finite State Machine              |

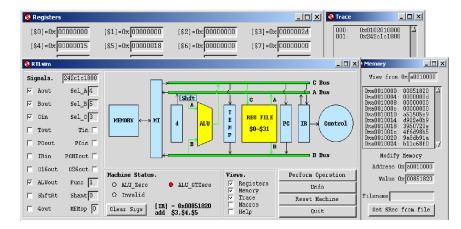

| 5.1  | Full Window of lc3uarch                |

| 5.2  | Animated Datapath                      |

| 5.3  | Animation Speed Menu                   |

| 5.4  | Opacity Menu                           |

| 5.5  | Controls                               |

| 5.6  | Registers                              |

| 5.7  | Changing Register Value                |

| 5.8  | Memory                                 |

| 5.9  | File Menu                              |

| 5.10 | Finite State Machine Information       |

| 5.11 | Console Output                         |

| 5.12 | Toggle Animations                      |

| 6.1  | Histogram of Responses                 |

# List of Tables

| 4.1 | Tabular View of Control Structure | 58 |

|-----|-----------------------------------|----|

| 6.1 | Totals of Survey Responses        | 76 |

# Foreword

This thesis has been formatted according to the style guide of the Department of Computer Science at Appalachian State University.

# Chapter 1 - Introduction

In the field of computer science, students study a broad range of topics, from abstract theoretical concepts to the logic gates printed on silicon. Unlike most courses, which focus primarily on either end of the spectrum, the topic of computer organization bridges the gap between high level computation and the hardware that makes the computations happen. Appalachian State University introduces this material in the sophomore level course "Introduction to Computer Systems." In this course, multiple layers of abstraction are presented, taking the student from the digital circuits to higher level programming languages. In its current form, the course uses Patt and Patel's textbook "Introduction to Computing Systems: From Bits & Gates to C & Beyond (2nd edition)." The textbook presents a hypothetical processor called LC-3. As the title's subtext suggests, the topics covered range from bit-wise operations to higher level languages. Since the described processor has never been built, execution of code written for the LC-3 must be done via simulation. Until the project presented by this thesis, no simulation existed for the microarchitectural level of the processor. This thesis documents the design, implementation, and evaluation of a graphical simulator targeted at the microarchitectural level of the LC-3 processor. The simulator is dubbed lc3uarch, short for "LC-3 Microarchitecture". The letter 'u' was chosen as a more easily typed version of the Greek letter  $\mu$ . This symbol is used as short-hand for the term "micro."

In Chapter 2, research is presented on the use of simulators, particularly in an educational setting. The literature covers why simulators should be used in education, the ways in which they can be used in a course, and the cognitive models created by experts in the field of educational simulation. The emphasis of the research is on visualization techniques and design of microarchitecture simulation.

Multiple simulators are reviewed in Chapter 3, detailing the features they offer and the basics of their structure and operation. These simulators target several topics covered in computer organization courses. Not all simulators reviewed share the same goals as lc3uarch, but the features and concepts are relevant and provide insight into designing a pedagogically sound tool.

A detailed view of the LC-3 processor is provided in Chapter 4. The definition of the Instruction Set Architecture is described, followed by the microarchitecture presented by Patt and Patel. The existing LC-3 related tools are briefly described as well. A more in-depth look at the design and implementation of lc3uarch is provided in Chapter 5. In particular, the design is presented in the context of the taxonomies revealed by the literature. More general elements are presented as well.

In Chapter 6, evaluation of lc3uarch's effectiveness is assessed through student surveys. Finally, Chapter 7 draws conclusions from the surveys, showing that the simulation is helpful in aiding student comprehension. The feedback also provides ways to improve the tool for future students.

# Chapter 2 - Uses of Simulation and Visualization

Simulation is broadly defined as an imitation of a process or system from the context of another process or system. The term has become commonplace, with computers serving as the platform on which other systems can be represented. Software simulators can be computationally taxing, originally requiring extensive resources to model anything of value. With advances in hardware capabilities and reduction of hardware prices, simulators have become increasingly common tools for solving problems and demonstrating otherwise inaccessible systems. The emphasis of this chapter is exploring the use of simulation and visualization within the computing domain, particularly computer architecture, with an emphasis on pedagogical needs.

In order to increase clarity, ambiguous terms are first defined. The term *simulation* in the context of computer science refers to the technique of representing the real world with a computer program. This generally applies to applications such as economic forecasting or weather modeling; however, the emphasis of this research is modeling computer architecture, digital logic, and computer code. The term *visualization* refers to a method of displaying the state and processes of the simulation. Thus, it is common that the visualization is often layered upon simulation software. The term *interface* is defined as the methods used to interact with the simulator. In most cases, the visualization method and interface are tightly coupled.

The contents of this chapter cover the use and general concepts of simulation. In some areas, brief references are made that will be expanded upon in later parts of the thesis. First, the advantages of simulation over hardware systems are discussed. This is followed by describing the use of simulation in university-level education. Further, the addition of visualization with simulation is described. Finally, the taxonomy and categorization of simulators and visualization is explored.

## 2.1 Advantages of Simulators

In recent years, Computer Science and Engineering departments have been moving away from hardware systems and towards simulation for course related systems. Of the many benefits cited, two major reasons stand out in nearly all reviewed texts: cost and accessibility [24, 12, 19, 1, 8, 4].

At the onset, the initial cost of hardware does not necessarily appear prohibitive, but several factors make long term costs significantly higher. First, the faculty must consider what system or systems are needed. For a single course, there may be need for examples of several different architectures, immediately multiplying the cost of the initial purchase. For most labs, the use of these systems must be shared between many students. Depending on the size of the department, this could imply a need for multiples of each system to allow students the necessary time to use the hardware. It is also necessary to consider the configuration and administration costs of the initial setup. This only addresses the initial purchase and configuration.

Over the life of the hardware, more costs are presented. As hardware ages, physical components break and must be replaced. Under optimal conditions with no repairs needed, power costs are continually incurred and routine maintenance is needed by trained administrator. As courses continue to evolve, new hardware needs must be addressed and the older systems must vie for lab space and administrative time. Thus, the costs continue beyond the initial purchase.

Another large advantage of using simulators instead of hardware is the accessibility of software. In a typical lab setting, students vie for time in front of a hardware system. At a minimum, this requires some administrative work to allot time to users. The users, in this context, include administrators maintaining the system, teachers creating coursework, and students doing the coursework. If a student cannot complete his or her work during allocated class time, it is the student's responsibility to vie for the remaining bit of time available on the system. These problems are compounded for students and faculty who commute long distances.

The use of simulation often resolves or largely mitigates the cost and accessibility problems of hardware. A simulator may run on multiple platforms, and each system may run multiple simulation instances. Further, a single physical system can generally run multiple simulated systems. This immediately reduces the total hardware needs drastically. If the system running the simulation software become antiquated or administrative costs become too high, simulation software can often be ported with little to no effort. This reduces the physical hosting costs in terms of space needed to keep old architectures around. The hardware costs already minimized, it is also worth noting that many of the simulators used for educational purposes are free to download, incurring no software costs beyond the operating system and supporting software.

The issue of accessibility is addressed by allowing students to access the simulator from multiple locations. No longer does the student need to sit in front of a bare-metal system to execute his or her work. At a minimum, the student should be able to access the simulator from any computer within the department's network. In most cases, that access is extended to any system with a network connection and a terminal client. Many educational simulators are also available to students for direct download, allowing the student to use the simulator at his or her own convenience [10].

For the needs of education, there are accessibility benefits beyond the logistics of where the simulation runs. For example, a simulation is easily slowed down or paused. This allows the user to review the state of all the components at a given time. On hardware systems this is a non-trivial task, if possible at all.

Overall, the case for using simulation versus hardware for education heavily leans towards simulation. Some situations may arise where hardware is still needed, but these would be exceedingly rare exceptions for required Computer Science courses.

# 2.2 Use of Simulators for Education

Many courses within a Computer Science curriculum can benefit from the use of simulation software. With the breadth of software packages that can be considered simulators, it is necessary to focus on a small subset for this thesis. The targeted subset is simulation of computer hardware. From university to university, the exact scope, name, and topics for the relevant courses vary. In spite of this variability, the reviewed literature commonly refers to three types of classes where simulation has been tried and generally found beneficial: Introduction to Computer Science, Introduction to Computer Organization and Assembly Language, and Advanced Computer Organization. Additionally, several authors have researched pedagogical approaches for integrating simulators with traditional teaching methods.

### 2.2.1 Targeted Courses

Three levels of courses in computer science curricula often use simulators. At the freshman level, Introduction to Computer Science can benefit from simulation of digital circuits. At the sophomore level, Introduction to Computer Organization and Assembly Language covers varying levels of abstraction of a CPU and supporting hardware. At the junior through graduate levels, Advanced Computer Organization expands on those topics and introduces new ideas relying on those fundamentals.

### 2.2.1.1 Introduction to Computer Science

In most departments, introduction to computer science covers the mathematical roots of computing. Among the topics covered, the tenets of Boolean and digital logic are particularly foundational. While this logic can be expressed solely through mathematical formulas, digital logic simulators can aid in demonstrating how the concepts apply in practice. The concepts of digital logic have a basal overlap with electrical engineering and computer engineering coursework. This has led some researching to borrow from the tools and pedagogical techniques of courses in these fields [6].

Introductory level courses also cover the basic ideas of computer architecture. A simulator demonstrating an over-simplified Von Neuman architecture can make the concepts clearer for an introductory student. These simulations are highly simplified, since the complexities of computer architecture quickly outgrow the scope of an introductory computer science course.

#### 2.2.1.2 Introduction to Computer Organization

Simulators are frequently used for courses covering the basics of computer organization and assembly language programming. A course of this type is taught to sophomore level students of computer science and is seminal in bridging the knowledge gap between what a computer can do and how it is actually done. Educators have found that both top-down and bottom-up approaches can be effective in exposing the relevant concepts [14, 24]. Since the top-down approach is accessible to a larger audience, it is used in the following paragraphs to extrapolate the ways simulation can be used for computer organizational courses, starting from a problem statement through multiple layers to execution of basic tasks.

The highest level of abstraction is expressed in terms of assembly language, a series of computational and control instructions. Individually, each instruction has a very minimal, but precise scope. For example, an assembly instruction may add two numbers. Assembly language code may also make decisions and navigate to other parts of the assembly code. These decisions are simple, such as "if this value is zero, go to this other instruction." While each instruction is minimal in scope, they can be aggregated to perform complex tasks.

The assembly language used by programmers is largely defined by the instruction set architecture. The *instruction set architecture* is defined as the complete specification of the interface between programs that have been written and the underlying computer hardware that must carry out the work of those programs [11]. This specification includes the data types allowed by the assembly language, what operations can be done, where the values can be stored, how many values can be stored, and how those values can be accessed. The ISA is a template for processor designers to follow. In current industry, the most common ISA is referred to x86. While processing power has advanced significantly, this same ISA has been at the root of processors created for several decades by multiple companies.

The physical implementation of the ISA specification is called the microarchitecture. This layer of abstraction is the primary focus of most computer organization courses. How the components are physically and logically arranged determines how quickly each operation can be completed. Patt and Patel compare the microarchitecture to an automobile [11]. The ISA equivalent of an automobile would consist of the placement and function of the pedals, the ability to turn, ability to move forward and backward, and the other common factors that define a car; however, the microarchitecture constitutes the way the components are arranged to make these things happen: the size of the engine, the transmission gear ratios, the braking mechanisms, the exhaust system. As an extension to this analogy, there are many trade-offs that take place when designing and arranging these components. A car with a larger engine will go faster, but it will consume more fuel. Similarly, a microarchitecture with a higher clock-speed will generally consume more electricity and may run at a higher temperature. A particular gear ratio in an automotive transmission will allow faster acceleration at the cost of top speed. Similarly, a microarchitecture with pipelining features will execute sequential code more quickly, but it may take a penalty when executing branches. The term datapath is often used interchangeably with microarchitecture, though it is actually a subset. The datapath refers to the collection and arrangement of components, without regarding the controls that "drive" execution through those components. For the purposes of this thesis, the terms are used synonymously.

The components used in the microarchitecture are composed of logical gates such as AND, OR, and NOT. While this topic is covered by most introductory computer science courses, computer organization courses often expand upon the concepts and demonstrate a more realistic application. The very specific details of digital logic are left to electrical engineering and computer engineering courses.

### 2.2.1.3 Advanced Computer Organization

Most universities offer courses covering the more advanced topics of computer organization. No consensus was found for how these topics are covered in terms of which courses contain what content. In most cases, the concepts are divided and covered as a small part of multiple courses, each with broader scope. One such example is the inclusion of memory caching concepts within Appalachian State University's courses called Systems I and Systems II. In larger departments, a concentration in computer system engineering is sometimes offered, with multiple courses expanding greatly on one particular subtopic such as parallelization [21]. The availability and structure of these courses varies greatly between universities and between undergraduate and graduate programs.

While simulators are often used in these courses, the focus is much narrower. The general purpose simulators for introductory courses focus on usability and accessibility, whereas the advanced simulators are driven by specific features. It is possible for simulators to be both intuitive and feature-rich, but the limited development time in an academic setting prevents most projects from achieving both goals simultaneously [22, 12, 24].

### 2.2.2 Pedagogical Styles and the Use of Simulators

In addition to the courses that can benefit from the use of simulators, particular pedagogical styles may benefit from the use of simulators. The styles may also determine the particular feature set required of a simulator [14, 21]. In addition to the variability of course needs, instructors may need to adopt a new style of teaching for a particular course.

In an inter-university study, it was found that Computer Organization courses have three main approaches [7]. The first approach is from an electrical engineering or computer engineering perspective, focusing on digital logic. The second approach is from a computer science perspective, focusing on assembly language and programming concepts. The last approach is to implement the ISA for a given architecture. Many simulators readily exist to assist with the first two pedagogical approaches, depending on the texts used in the course. Implementation of the ISA would generally require the student to create a simulator of his or her own. If the students do not implement their own simulators, they may use an advanced circuit design tool to implement the ISA.

According to Stenstrom and Dahlgren, computer organization courses increasingly focus on trade-off analysis [21]. With the aid of a simulator, students can quickly go through cycles of making changes, testing, and quantitatively measuring the effects. Without simulation, the cycles' effects would have to be calculated by hand or executed on hardware, slowing down the evaluation of the changes.

Regardless of the pedagogical style used, all sources agreed that simulators aid in student comprehension of the material. In several instances, the added comprehension was attributed to allowing "hands-on" learning [8, 10, 9]. While this seems intuitive, this theme being explicitly stated by multiple authors bolsters the anecdotal evidence.

# 2.3 Simulation Visualization and Interfaces

Thus far, simulators have been discussed in abstract terms, in what they can accomplish and where they can be used. These ideas neglect the relationship to the user. Equally important is how information is displayed and how the user interacts with them.

At a bare minimum, the user must see the final result of the simulation. This outcome assumes that the use of the simulation is goal-oriented not pedagogically oriented. Simulators based on assembly code often allow intermittent results to be displayed, based on setting breakpoints at particular lines of code. The code is then executed up until that point, and the simulator waits for further instructions from the user. The user can then display the state of the various components and proceed with the simulation. The method of continuing varies between simulators, some allowing the user to step a single instruction at a time, running until the next breakpoint is reached.

Simulators of the microarchitecture or hardware level often advance in terms of clock cycles instead of assembly instructions. The processing of a single instruction takes multiple clock cycles to load the appropriate values in registers, to interpret the instruction, to gather data, to execute the instruction, and finally to store the result. An assembly level simulator will commonly do all this in one step, glossing over details that are only relevant on an organizational level.

How the data is displayed varies between simulators. A simple method of displaying data is via a *pretty printer* which represents the data as formatted text. This technique is commonly used for assembly level simulators focused on the debugging and results of a program. For digital logic and microarchitecture simulators, it is more common to see graphical displays. In a graphical display, the screen is divided into multiple sections, each representing a different facet of the underlying simulation. What components are displayed and how they are arranged is largely dependent on the focus of the simulation.

The user interface and the visualization method are often codependent and highly dependent on the goals of the simulation. For example, a digital logic simulator designed for exploratory learning will generally allow the user to click through the interface and change the virtual wiring during a simulation. In a similar digital logic simulator designed for demonstrative purposes, the user would not be able to click through the interface to change wiring configuration. Another simulator may allow both approaches, each in a separate mode. The introduction of such modality increases the complexity of developing and using the simulator. For this reason, designers often opt to avoid particular features, even if they have pedagogical value.

# 2.4 Taxonomy and Categories of Educational Simulators

Before using and reviewing an existing simulator, it is helpful to have an understanding of how it can be categorized and classified. This allows a level field when comparing simulators by feature and overall goal. Several authors offer taxonomies for informed simulator selection and/or design [24, 15, 25].

### 2.4.1 Categories of Simulators

Wolffe, Rucik, Osborne, and Holliday have undertaken the task of reviewing and aggregating existing simulators [24], with the goal of listing all educationally relevant simulators in a single place. In the process of reviewing simulators, seven categories were defined, based on what is being simulated. The primary motivation for compiling this list is to provide educators a simpler method for finding simulators for particular topics. According to the authors, these seven categories cover all current simulators used for university level education.

### 2.4.1.1 Historical

Historical simulators represent older architectures that are either scarce or non-existent in the present day. It is common for a historical architecture to be used to provide a demonstration of a particular concept for which it became famous. No specific historical simulators were reviewed for this thesis, but Wolffe et al. provide a list including PDP-8, PDP-11, Turing Machine, Babbage Analytical Engine, and the Enigma machine [24]. Individuals familiar with the history of computing will note that each of these is an important milestone in the advancement of CPU design.

### 2.4.1.2 Digital Logic

The focus of digital logic simulators is on basic elements, circuit analysis, timing systems, and low level storage structures. These simulators are used with a bottom-up pedagogical approaches, commonly for computer engineering and electrical engineering courses. DLSim 3, JLS, and Logisim are all educational digital logic simulators and are reviewed in more depth in Chapter 3 [16, 12, 6].

### 2.4.1.3 Simple Hypothetical Simulators

With the increasing complexity in real machines, it is often necessary to study a simplified counterpart. Simulators in the hypothetical category vary in complexity, depending on the target audience. At the simplest level, Knob & Switch Computer and Little Man Computer are designed for high school or freshman level students who have little experience with computer hardware [4, 27, 26]. Both of these are described in Chapter 3. Targeting students with slightly more background knowledge, TRISC, EasyCPU, MarieSim, and Micro provide more details about the internal components of the architecture [3, 26, 10, 9]. While these simulators target the same level of student, their approaches for conveying information vary. Both EasyCPU and MarieSim are covered in more depth in Chapter 3. An advantage of using hypothetical simulators is that fine-grain details can be omitted, thus preventing possible confusion for students.

### 2.4.1.4 Intermediate Instruction Set

Intermediate instruction set simulators extend the functionality of simple hypothetical simulators. In these simulators, additional concepts are introduced, such as memory addressing modes, additional instructions, and memory modeling. There is no hard delineation between hypothetical and intermediate simulators, so there is potential for a particular simulator to belong in a gray area in between. Some intermediate simulators target assembly level programming such as GSPIM and MARS [2]. Others target elements of microarchitecture, such as SimICS and EASE [21, 18].

## 2.4.1.5 Advanced Microarchitecture Simulators

Advanced microarchitecture simulators add even more complexity, often exposing some method of modifying the datapath or control store. The ability to modify the datapath allows the user to perform trade-off analysis, comparing how the implementations perform under different configurations. MicroTiger allows complete datapath reconfiguration, including rearranging components, changing connections, and modifying the microcode [22]. Pep8CPU, Mic-1, and CPU Sim do not allow rearranging components but allow the user to modify the control store by editing the microcode [23, 17, 19, 20]. RTLSim takes a more modest approach, allowing the user to set the control signals during each clock cycle [26]. The SLEEP simulator does not directly use the control store, but it allows the user to create components with behavior specified by Java code [13]. Once created, the components can be reused and combined into the datapath. Chapter 3 covers Pep8CPU and MicroTiger in more depth.

### 2.4.1.6 Multiprocessor

Multiprocessor simulators address the unique challenges of executing a program in a multiple processor environment. To demonstrate these unique elements, the simulators require an enhanced set of features, such as shared memory and simultaneous execution of instructions. Due to the complexity of multiprocessor programming, this category of simulators can be difficult to learn and use. No multiprocessor simulators were reviewed for this thesis, but Wolffe et al. list ABSS, MINT, Proteus, RSIM, and SimOS as members of this category [24].

#### 2.4.1.7 Memory Simulators

Nearly all simulators reviewed contain a memory array as an integral component of the architecture; however, memory simulators focus solely on memory related concepts, often to the exclusion of instruction execution. The concepts covered include hierarchical caching level, cache sizes, and memory associativity. Since this specialized category does not relate to the topic of this thesis, no simulators were reviewed. Wolffe et al. mention Cacheprof, Cache Simulator, CACTI, Dinero IV, RPIMA, and Xcache as examples of memory simulators [24].

### 2.4.2 Taxonomy of Program Visualizations

Roman and Cox present a general taxonomy for program visualization [15]. Their taxonomy is broad, covering far more than simulations and computer architecture. The taxonomy applies reasonably well to the needs of computer architecture simulation, although the breadth is too generic in some places. The authors present five components in their taxonomy.

### 2.4.2.1 Scope

The scope defines which conceptual elements of a program are intended to be displayed. In architecture simulation, the scope usually targets the assembly layer, ISA layer, microarchitecture layer, or some combination of these. Generically, the authors present several sub-categories of scope including the code, the data state, the control state, and the behavior. The selection of the scope determines how the other parts of the visualization will form.

### 2.4.2.2 Abstraction

The abstraction defines what data is to be displayed. Applied to architecture simulation, this aspect of the taxonomy determines which components will be displayed. For example, the abstraction can include simple components such as logic gates or more complex components such as multiplexers. The choice of which components to include is influenced by the targeted scope and granularity of the simulation. Depending on which components are used, the level of abstraction will determine the behavior of the simulation.

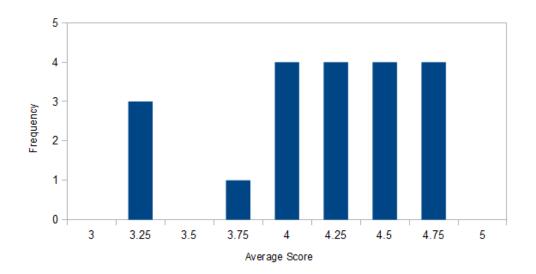

### 2.4.2.3 Specification